SUS Hardware Description Language

The raison d'être of this project stemmed from my Dedekind work. I did the Hardware Design for this project with plain SystemVerilog, and in doing so bumped against every possible issue that occurs when doing so. I found that the existing repertoire of languages is too difficult to work with to build meaningful hardware accelerators. On the other hand, HLS (or High Level Synthesis) takes away so much freedom from the hardware design process, and more importantly, takes away the insight into what hardware is actually generated. So some middle-road is needed. SUS is my (perhaps ill-fated) attempt at making a language that maintains the control we need, while being useable enough to do productive work with.

I'm working on this actively during my PhD position at the Paderborn Center for Parallel Computing. And the main goal is to see adoption of it, to replace the HLS code we currently use at PC2.

More information can be found on the repository: https://github.com/pc2/sus-compiler

It also has a website now: https://sus-lang.org, or a more trendy https://sus.rocks.

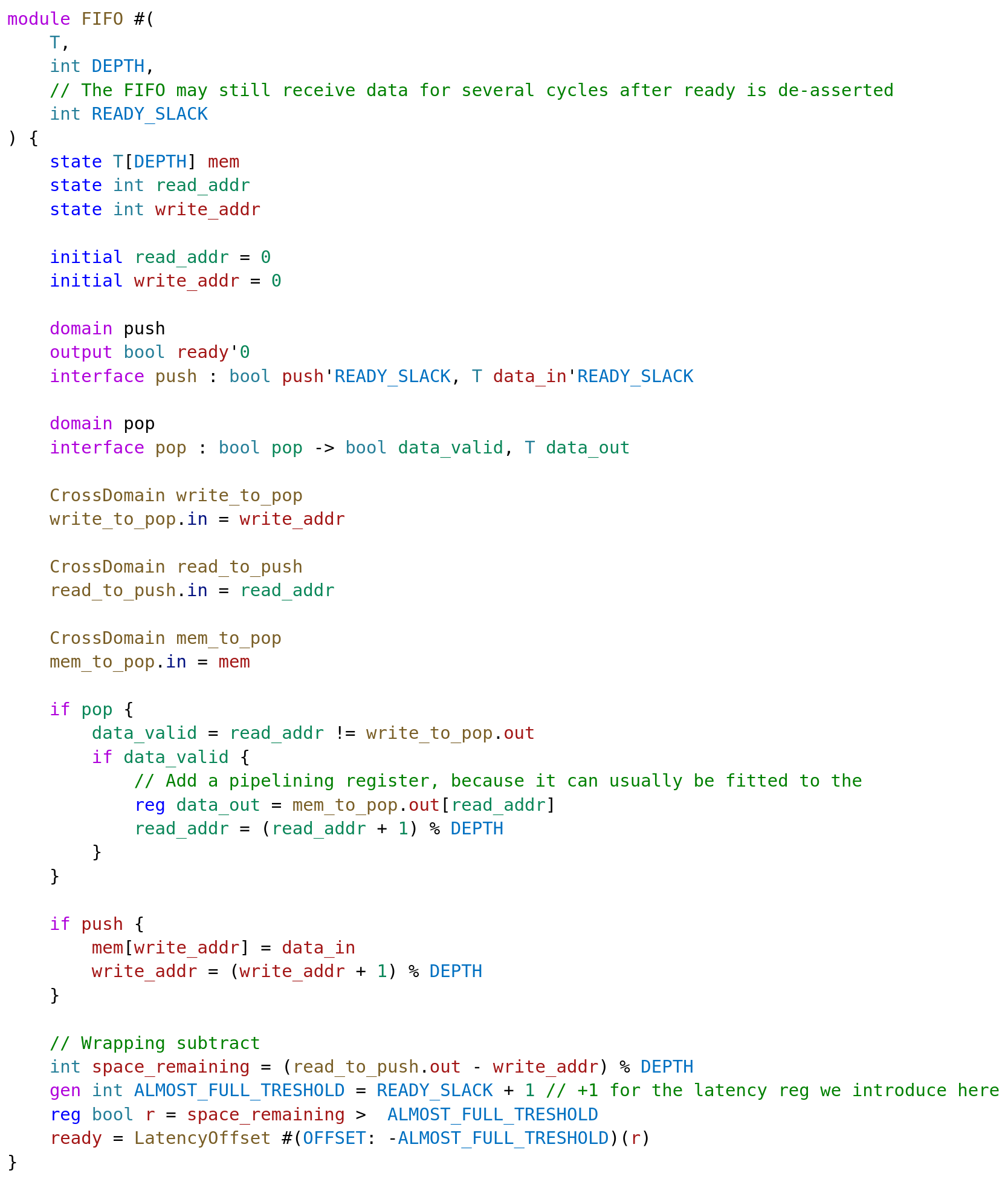

Sample SUS Code